封装体叠层(PoP,Package-on-Package)技术

在逻辑电路和存储器集成领域,封装体叠层(PoP)已经成为业界的首选,主要用于制造高端便携式设备和智能手机使用的先进移动通讯平台。移动便携市场在经历2009年的衰退之后,已经显示反弹迹象,进入平稳增长阶段,相比而言,智能手机的增长比其它手机市场更快,占据的市场份额正不断增加。与此同时,PoP技术也在移动互联网设备、便携式媒体播放器等领域找到了应用。这些应用带来了对PoP技术的巨大需求,而PoP也支持了便携式设备对复杂性和功能性的需求,成为该领域的发动机。像应用处理器或基带/应用存储器组合这样的核心部件,其主要的生产企业都已经或计划使用PoP解决方案(图1)。

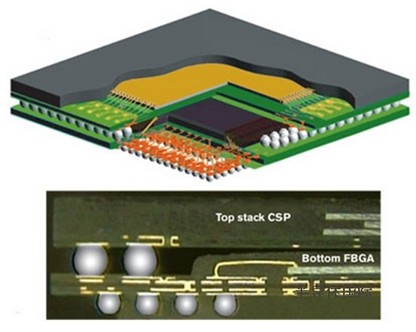

图1. 尽管业界逐渐转向使用倒装芯片技术,但引线键合依然具有成本优势,并在PoP技术中得以继续使用。

PoP技术演化

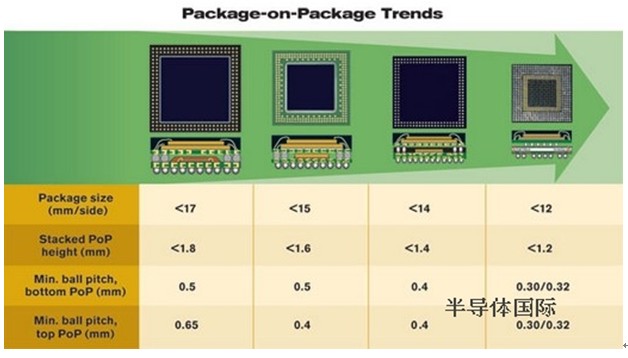

对于底层PoP封装来说,引线键合正迅速被倒转焊技术所取代。对更小封装尺寸的要求,推动着焊球节距的不断缩小,目前在底层PoP中,0.4 mm的焊球节距已经非常普遍。与此同时,顶层封装的DRAM芯片,以及包含闪存的DRAM芯片,都有更高速度和带宽的要求,这对应着顶层封装需要具有数目更多的焊球。由于同时要求更大焊球数目和更小封装尺寸,因而降低顶层封装的焊球节距非常必要。在过去0.65 mm的节距就足够了,而现在需要使用0.5 mm的节距,而0.4 mm的节距也即将上马被采用。

封装间焊球节距的缩小带来很多问题。首先,更小的焊球节距要求更小的焊球尺寸,而且顶层封装与底层封装的间隙高度在回流之后也会更小。当然,这影响底层封装之上允许的器件最大高度。目前,在这一方面所作的努力大部分都是向倒装芯片和更密封装间互连转变,以满足对更小封装尺寸和叠层高度的要求(图2)。

图2. 随着PoP技术的演变,封装体的尺寸、高度和焊球节距的发展趋势。

退一步来说,尽管包含逻辑处理器的底层封装体正明显地从引线键合向倒装芯片技术转变,但引线键合技术并未就此退出历史舞台,依然还是顶层存储器件封装的标准互连方法。而且,引线键合技术依然具有成本优势,特别是在使用铜线的情况下。底层封装在集成叠层器件时还需要使用这一技术,此外,引线键合对于一些底层封装来说依然还是一个必需的要素。

引线键合连接的底层封装使用顶部中央模塑开口(TCMG)的模塑技术完成包封,以保证底层封装体边缘没有环氧模塑混合物(EMC),从而顶面边缘的焊盘得以暴露用于实现与顶层封装体的互连。模塑封帽的厚度必须可以覆盖整个片芯以及片芯表面的连线。如果顶层封装的焊球节距从0.65 mm缩小到0.5 mm,在所要求的0.22 mm的模塑封帽高度限制下,实现引线键合器件的塑封将会很具挑战性。芯片边缘处引线键合所要求的键合壳层或区域,同样也会成为限制封装尺寸降低的障碍。尽管像叠层芯片或面向中端移动市场的应用,可能会继续使用引线键合TCMG型底层封装,但大部分的未来应用将会转向使用倒装芯片技术以进一步缩小封装尺寸、降低顶层封装焊球节距,并提高封装的密度和性能。

采用倒装芯片的底层封装

在底层封装中使用倒装芯片技术,对应的开发及引入方式可以分为两类,分别是裸片型和模塑型。裸片型倒装芯片底层封装在本质上类似于薄而小的倒装芯片BGA。目前最“称意”的PoP尺寸不要超过14 × 14 mm,最好是12 × 12 mm,而且封装间焊球节距为0.5 mm。裸片型封装已得到充分开发,并用于大批量生产。为了实现这种应用,倒装芯片器件的组装高度必须大约为0.18 mm。这可以通过将倒装芯片器件厚度减薄到0.10 mm来实现,这在目前的加工能力下没有任何问题的。

一个主要的问题是如何在回流过程中控制封装体翘曲变形的程度。在表面贴装(SMT)过程中,首先将底层封装放置在PCB板丝网印刷的焊膏之上,接着顶层封装沾取助焊剂并放置在底层封装上,之后两个封装在回流炉中同时实现与PCB(还包括PCB上组装的其他所有组件)的回流。目前量产的所有PoP都使用无铅焊球,回流最高温度可以达到260ºC,而且在炉子中没有氮气保护。对应SMT工艺需要具有足够高的鲁棒能,以保证非常低的每百万单位缺陷数目(DPM),提高成品率水平,因而需要严格控制回流操作中PoP的翘曲变形程度,以获得最高的成品率。

对于0.5 mm的封装焊球节距,希望回流过程中所有封装的翘曲变形不超过0.06 mm。这一目标可以通过选择合适的衬底厚度和内核基板材料来实现,特别是对于12 × 12 mm的芯片来说更是如此。而对于14 × 14 mm的芯片,这变得比较困难,但可以通过使用低热膨胀系数(CTE)的衬底内核材料来实现。衬底材料供应商已经开始相应动作,为满足这些要求推出低CTE叠层衬底材料。

大尺寸解决方案

顶层封装体采用0.5 mm焊球节距,其尺寸逐渐超过12 × 12 mm,而且顶层焊球节距正逐步缩小到0.4 mm(图3),在这样的趋势下,模塑型底层PoP逐渐得以应用。模塑型底层PoP也可以实现芯片叠层,包括将引线键合器件叠层在倒装芯片上等情况。模塑型底层PoP以阵列的形式进行模塑处理,并类似传统小节距球栅阵列(FBGA)封装被切割分离,对应EMC能够扩展到封装边缘,有助于控制封装的翘曲变形程度。

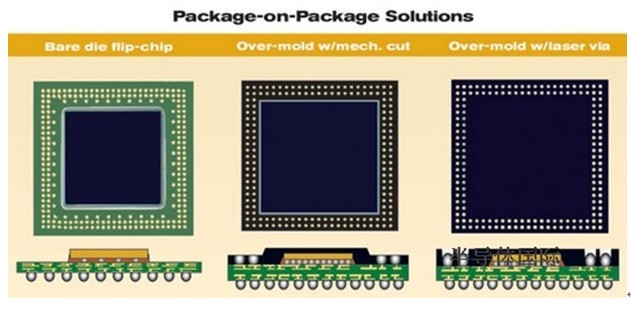

图3. 存在多种窄互连节距PoP解决方案,包括裸片型倒装芯片方案、采用机械切割的模塑方案以及采用激光打孔的模塑方案。

一个显而易见的问题是如何暴露出顶层边缘的焊盘,这样才能通过焊球与顶层封装的互连。目前开发了两种方法实现这一目标,分别是机械切割和激光烧蚀。使用机械切割的方式,去除模塑之前,底层封装上表面边缘焊球上覆盖的EMC材料。这样封装边缘的EMC厚度会被降低,达到使焊球暴露以满足顶层封装回流的要求。必须严格控制边缘位置处EMC材料的高度或厚度,因为这会影响焊球的暴露直径、暴露焊料量以及回流后与顶层封装的焊料融合质量。这种类型的底层PoP已经被开发出来,但还没有广泛应用于生产。

使用激光烧蚀暴露封装上表面边缘焊球方法,在底层PoP中正获得越来越多的关注。激光烧蚀或激光钻孔已经在封装衬底制造中获得了广泛应用,而目前这一技术又被用于在底层封装上制作EMC通孔。

同样地,控制通孔制作对SMT过程中可以无缺陷地从顶至底完成PoP回流至关重要。通孔与焊球的对准精度、模塑帽上部的外孔直径(OHD)和暴露焊球的内孔直径都必须进行优化并严格控制。目前已经在0.5 mm封装间焊球节距和很多大尺寸(样品尺寸)SMT试验中显示了所需加工能力,正在进行板级可靠性研究来探索可接受的DPM水平。对于这种激光通孔型底层封装,0.4 mm的封装焊球节距正在开发中。

对于0.4 mm的封装互连焊球节距,翘曲变形必须控制在0.05 mm以下。激光通孔模塑技术与低CTE衬底配合的方案已在开发阶段。可以考虑使用裸片倒装芯片底层PoP,但为了适应0.4 mm封装接口节距所需的更小封装间距,倒装芯片器件将会需要被减薄到约0.06 mm,这样对应的组装高度约为0.13 mm。对于这么薄的裸片倒装芯片器件,如何操作和测试都将是棘手的问题。然而,裸片倒装芯片PoP对应着最低的组装成本。0.4 mm PoP接口节距的关注热点在于选择激光通孔的类型。一般认为,通过开发和使用倒装芯片模塑底部填充(MUF)以及其他低成本倒装芯片方法,可以降低这种封装的总体成本。

未来的PoP

对于小而薄PoP解决方案的需求将会继续,预计PoP将会在目前市场份额的基础上在其他低成本手机和其他消费设备中得以应用。为满足这些需求,正在开发使用更小PoP互连节距的更薄PoP解决方案(图4)。使用与硅器件本身性质更加匹配的材料以降低翘曲变形,这种更薄的高密度衬底技术也在评估过程中。甚至使用包含穿透硅通孔(TSV)的硅基衬底方案以实现超薄PoP叠层也在考虑范围内。TSV可以实现高密度薄型存储器叠层,在不远的将会有可能会在顶层PoP存储器叠层中得以使用。目前已经开发出扇入型PoP技术,实现高密度小节距封装间互连(已经可以实现0.4 mm的顶层封装节距)。

图4. 未来的PoP解决方案将会实现更高互连密度、更薄体积的叠层。

下一代三维扇出型圆片级封装(FOWLP)技术,也就是被广泛称作嵌入性圆片级BGA(eELB)的封装技术,可以实现超薄PoP模块,正受到越来越多的关注。这种eWLB封装,在封装的双面使用再布线层,并使用通孔穿透封装边缘处塑料扇出区域,可以实现约0.25 mm的封装体厚度,在封装体内可以并排放置多个芯片,而且可以实现节距小于0.4 mm的高密度封装接口,从而可以允许小于0.15 mm的封装间隙。使用这种技术,可以实现高度低于1.0 mm、尺寸小于12 × 12 mm的封装体积。